ters. This system is stable since the cascaded EDFAs can automatically control the soliton power level. Although strong interaction may occur after propagation over more than

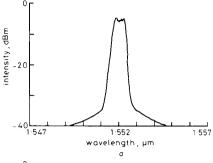

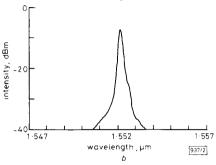

Fig. 2 Output spectra of the MQW DFB LD when gain switching technique is applied

a Without FPR

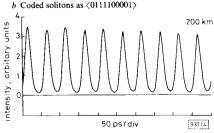

Fig. 3 Coded soliton pulse waveforms at 20 Gbit/s transmitted over  $200\,\mathrm{km}$

937/3

50 ps/div

a Coded solitons as <0011001100>

Fig. 4 20 GHz soliton transmission over 200 km

500 km, it can be said that soliton communication has great potential for realising ultrahigh bit-rate optical communication systems.

In summary, we have shown that it is possible to send a 20 Gbit/s soliton signal over 200 km using erbium-doped fibre amplifiers. This means that EDFAs are very promising as soliton amplifiers.

The authors would like to express their thanks to Drs. T. Nozawa and K. Noguchi of NTT Optoelectronics Laboratories for providing an excellent LiNbO $_3$  optical modulator. Thanks are also owing to Drs. S. Shimada and H. Ishio for fruitful discussion and comments on a comparison between ordinary high bit-rate intensity modulation/direct detection systems and the present soliton transmission systems.

3rd August 1990

M. NAKAZAWA K. SUZUKI E. YAMADA Y. KIMURA

NTT Transmission Systems Laboratories Lightwave Communication Laboratory Tokai, Ibaraki-Ken 319-11, Japan

## References

- 1 MEARS, R. J., REEKIE, L., JAUNCY, J. M., and PAYNE, D. N.: 'Low-noise erbium-doped fibre amplifier operating at 1·54 μm', Electron. Lett., 1987, 23, pp. 1026–1028

- DESURVIRE, E., SIMPSON, J. R., and BECKER, P. C.: 'High-gain erbium-doped travelling-wave fiber amplifier', Opt. Lett., 1987, 12, pp. 888-890

- 3 KIMURA, Y., SUZUKI, K., and NAKAZAWA, M.: '46-5 dB gain in Er<sup>3+</sup>-doped fibre amplifier pumped by 1-48 µm GaInAsP laser diodes', Electron' Lett., 1989, 25, pp. 1656-1658

- NAKAZAWA, M., KIMURA, Y., and SUZUKI, K.: 'Soliton amplification and transmission with Er<sup>3+</sup>-doped fibre repeater pumped by GalnAsP laser diode', *Electron. Lett.*, 1989, 25, pp. 199-211

NAKAZAWA, M., SUZUKI, K., and KIMURA, Y.: '3-2-5 Gbit/s, 100 km

- 5 NAKAZAWA, M., SUZUKI, K., and KIMURA, Y.: 3-2-5 Gbit/s, 100 km error-free soliton transmission with erbium amplifiers and repeaters', IEEE. Phot. Tech. Lett., 1990, 2, pp. 216-219; KUBOTA, H., and NAKAZAWA, M.: 'Long-distance optical soliton transmission with lumped amplifiers', IEEE J. Quantum. Electron., 1990, QE-26, pp. 692-700

- 6 OLSSON, N. A., ANDREKSON, P. A., BECKER, P. C., SIMPSON, J. R., TANBUN-EK, T., ROGAN, R. A., PRESBY, H., and WECHT, K. W.: '4 Gbit/s soliton data transmissin experiment'. Proc. Opt. Fiber Commun. Conf., San Francisco, USA, 1990, PD4

- 7 MARSHALL, I. W., SPIRIT, D. M., BROWN, G. N., and BLANK, L. C.: 20 Gbit/s 100 km non-linear transmission with semiconductor source. Proc. Opt. Fiber Commun. Conf., San Francisco, USA, 1990, PD6

- 8 NAKAZAWA, M.: 'Propagation and amplification of ultrashort optical soliton pulses in erbium-doped fibers for very high speed communication'. Top. Meeting on Ultrafast Phenomena'90, Monterey, California, ThA2, 1990

- 9 SUZUKI, K., and NAKAZAWA, M.: 'Automatic optical soliton control using cascaded Er<sup>3+</sup>-doped fibre amplifiers', *Electron. Lett.*, 1990, 26, pp. 1032–1034

## HIGH-PERFORMANCE ALGORITHMIC SWITCHED-CURRENT MEMORY CELL

Indexing terms: Memories, Current mode

A new high-performance algorithmic switched-current memory cell with greatly improved charge injection performance is described. The new cell uses algorithmic means to achieve an improvement in charge injection of two orders of magnitude and does not rely on matching.

Introduction: There is tremendous interest in the application of switched-current (SI) techniques to the design of analogue filters and data convertors. SI techniques offer major advantages over conventional switched-capacitor techniques in the

ELECTRONICS LETTERS 13th September 1990 Vol. 26 No. 19

1593

The switched-current (SI) memory cell, also known as the current copier, was initially conceived 1-4 to overcome the inherent matching limitations of continuous time current mirrors. Initially, the cell found application in high performance D/A convertors<sup>2</sup> and more recently as a delay element for the realisation of analogue filters.<sup>5</sup> Many new applications are currently under investigation.<sup>6</sup> In this letter we propose a new high performance algorithmic SI memory cell incorporating a novel switching arrangement to enhance current transfer accuracy.

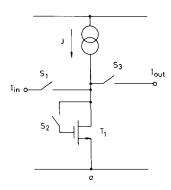

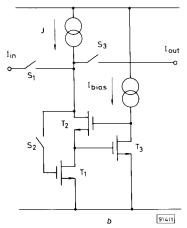

Existing memory cells: The basic switched-current memory cell¹ is illustrated in Fig. 1a. At  $\phi_1$ , switches  $S_1$  and  $S_2$  are closed,  $S_3$  open.  $T_1$  is thus diode-connected, and a drain-source current of  $J+I_{in}$  will charge its gate-source capacitance,  $C_{gs}$ . The  $V_{gs}$  established is that required to maintain the current  $J+I_{in}$  when the input is removed, thus memorising the input. At  $\phi_2$ ,  $S_1$  and  $S_2$  are open,  $S_3$  closed. Since  $T_1$  maintains a drain current of  $J+I_{in}$  the output current is  $-I_{in}$  which is an inverted direct copy of the input. Note that the output of the cell is a discontinuous copy of the input. For 'continuous' operation two basic cells may be cross-coupled to form a dynamic mirror.  $^4$

Fig. 1 Basic current memory cell

- a Single transistor memory

- b Regulated cascode memory

1594

There are two primary problems with this basic SI cell. The channel length modulation effect causes an error in the output, if the  $V_{DS}$  of  $T_1$  is not the same in the sampling and retrieval phases. The second is that when  $S_1$  and  $S_2$  open, a proportion of their channel charge is dumped onto the  $C_{gs}$  of  $T_1$ , causing a  $\Delta V_{gs}$  and hence an output current error. The charge injection from  $S_1$  can be eliminated by ensuring that  $S_2$  opens slightly before  $S_1$ ; which can be achieved by delaying the falling edge of  $S_1$ 's clock.

There are several techniques for tackling the channel length modulation problem,  $^{7.8}$  of which the use of a cascoded or a regulated cascode transconductor  $^8$  appears the most promising. A SI memory cell based on the regulated cascode is shown in Fig. 1b. It has been shown that, by operating the storage transistor of the regulated cascode in its saturated region, an improvement of three orders of magnitude is possible in the output resistance of the cell. An improvement of two orders of magnitude is still possible with unsaturated operation, which gives a reduced  $g_m$ , which is constant with  $I_{DS}$ , an advantage from the charge injection viewpoint.

$I_{DS}$ , an advantage from the charge injection viewpoint. With the vast improvement in output resistance possible using cascoding, charge injection has become the dominant performance limitation. There are a number of techniques for reducing the effects of charge injection. The most common rely on various matching mechanisms to achieve charge injection cancellation, such as the use of dummy switches. We propose an algorithmic memory cell which achieves cancellation without the need for matching, resulting in a significant performance improvement.

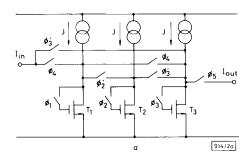

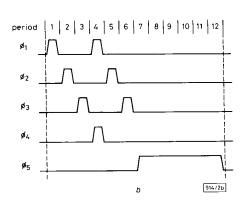

Algorithmic memory cell: Fig. 2a shows the proposed algorithmic memory cell, which uses five phases and three basic memory cells. The required clocking scheme is illustrated in Fig. 2b; it should be noted that phases  $\phi_2'$  and  $\phi_3'$  (not shown) are the same as  $\phi_2$  and  $\phi_3$  with a delayed trailing edge to avoid additional charge injection.

Fig. 2 Algorithmic memory cell

- a Structure

- b Timing diagram

ELECTRONICS LETTERS 13th September 1990 Vol. 26 No. 19

The concept of the circuit is to access the charge injection error of a memory cell, invert it and then pass it through the same cell again. The algorithmic nature of this process ensures that the charge injection error is cancelled without the need for matching.

Ц

In periods 1 and 2 the charge injection error of the first two cells is accumulated. In period 3 the charge injection error of the third cell is added. This is done in the presence of the input current,  $I_{in}$ , to ensure that the  $g_m$  of  $T_3$  is the same as it will be in the output phase,  $\phi_5$ . In period 4 the output of the third cell is summed with the input,  $I_{in}$ , leaving just the accumulated charge injection errors to be sampled by the first cell. The uneven number of signal inversions around the loop ensures that the charge injection error of the first cell in period 1 cancels with its charge injection in period 4. The same cancellation occurs in the second cell and then again in the third cell, where the input signal is reintroduced. Finally, during periods 7–12, the input current,  $I_{in}$ , is output together with any residual error. Thus using the proposed cell, charge injection errors have been cancelled, according to the following relationship:

$$I_{out} = -I_{in} - (\delta_{14} - \delta_{11}) + (\delta_{25} - \delta_{22}) - (\delta_{36} - \delta_{33}) \quad (1)$$

where  $\delta_{ij}$  is the charge injection in the *i*th cell during period *j*.

Simulated results: The performance of the proposed cell was simulated using HSPICE and the parameter set of a typical  $2\,\mu m$  N-well CMOS process. All the switches used were  $2/2\,\mu m$  (W/L); the memory transistors were  $60/20\,\mu m$  in the basic cell,  $100/20\,\mu m$  in the saturated regulated cascode and  $25/20\,\mu m$  in the basic cell,  $100/20\,\mu m$  in the saturated regulated cascode and  $25/20\,\mu m$  in the unsaturated regulated cascode. The bias current, J, used in all cases was  $100\,\mu A$  and the width of each clock pulse was  $400\,n s$ .

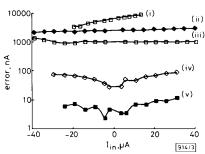

The improvement in charge injection error offered by the proposed algorithmic memory cell is illustrated in Fig. 3,

Fig. 3 Charge injection performance

- (i) Basic cell with single transistor

- (ii) Basic cell with saturated regulated cascode

- (iii) Basic cell with unsaturated regulated cascode

(iv) Algorithmic cell with saturated regulated cascode

- (v) Algorithmic cell with unsaturated regulated cascode

where its performance is compared with that of the basic cell, using a single transistor (Fig. 1a) and a regulated cascode (Fig. 1b), with its memory transistor in saturated and unsaturated operation. To give a strict comparison the performance of the basic cell is compared with that of the algorithmic cell (Fig. 2a) with its basic transistors also replaced by regulated cascodes, so that the main source of error is charge injection. It can be seen that the proposed cell offers a significant improvement of about two orders of magnitude in charge injection over the equivalent basic cell, when an unsaturated regulated cascode is used. Since the error currents are being stored by the basic cells in one phase and cancelled in another, the cell current will vary slightly giving rise to a small  $g_m$  change and hence to a small residual error. When an unsaturated regulated cascode is used the  $g_m$ s remain constant and this source of secondary error is eliminated.

In the above comparison, we have not attempted to compare the performance of the proposed algorithmic cell with the charge injection minimisation schemes currently available. 7.9 This is because the proposed cell, envisaged as a direct replacement for the basic cell, offers improved charge injection performance. Charge injection minimisation schemes may still be applied to yield even better performance.

The above improvement in charge injection performance has been achieved at the cost of increased area and power consumption. In typical system applications much of the chip area will be occupied by digital logic and consequently the price paid is not prohibitive.

Using the same basic cell, the proposed cell operates at one sixth the speed of the basic cell, because of the use of more complex clocking than before. Thus the proposed cell offers a significant improvement in the accuracy, with only a slight loss in speed. To assess the speed/accuracy trade-off of the new cell, its settling time was simulated, with a  $10\,\mu\text{A}$  input current to 0.01%, using an unsaturated regulated cascode memory cell. The settling time for the cell was found to be  $123\,\text{ns}$ , giving a maximum operating frequency of  $650\,\text{KHz}$  for the new cell and  $3.9\,\text{MHz}$  for the basic cell. In this instance using the new cell has improved the charge injection by a factor of 46, thus giving a significant speed/accuracy improvement of  $7.7\,\text{times}$ .

Conclusions: A new high performance algorithmic switchedcurrent memory cell has been proposed. This cell offers a significant improvement in the magnitude of charge injection and consequently the speed/accuracy ratio compared with that of the basic cell architecture. The accuracy of the cell is open to further improvement if additional cancellation techniques are applied or if high frequency performance is sacrificed.

The new cell is envisaged as a direct replacement for the basic cell and as such will find wide application in filtering and data conversion applications.

Acknowledgments: The authors gratefully acknowledge J. B. Hughes of Philips Research Labs (Redhill) for useful discussion related to this work. The financial support of Philips Research Laboratories (Redhill) Ltd and the SERC are also gratefully acknowledged.

C. TOUMAZOU

1st August 1990

N. C. BATTERSBY C. MAGLARAS

Department of Electrical Engineering Imperial College of Science, Technology and Medicine London SW7 2BT, United Kingdom

## References

- DAUBERT, S. J., VALLANCOURT, D., and TSIVIDIS, Y. P.: 'Current copier cells', Electron. Lett., 1988, 24, pp. 1560–1562

GROENEVELD, W., SCHOUWENAARS, H., and TERMEER, H.: 'A self cali-

- 2 GROENEVELD, W., SCHOUWENAARS, H., and TERMEER, H.: 'A self calibration technique for monolithic high-resolution D/A converters'. ISSCC Digest of Technical Papers, Feb. 1989, pp. 22-23

- ISSCC Digest of Technical Papers, Feb. 1989, pp. 22-23

HUGHES, J. B., BIRD, N. C., and MACBETH, I. C.: 'A new technique for analog sample data signal processing'. Proc. IEEE ISCAS 1989, May 1989, pp. 1584-1587

- 4 WEGMANN, G., and VITTOZ, E. A.: 'Very accurate dynamic current mirrors', Electron. Lett., 1989, 25, pp. 644-646

5 HUGHES, J. B.: 'Switched-current filters', in TOUMAZOU, C., LIDGEY, F.

- 5 HUGHES, J. B.: 'Switched-current filters', in TOUMAZOU, C., LIDGEY, F. J., and HAIGH, D. G. (Eds) 'Analogue IC design: the current-mode approach' (Peter Peregrinus Ltd, 1990)

- 6 VALLANCOURT, D., and DAUBERT, S. J.: 'Applications of current-copier circuits', in TOUMAZOU, C., LIDGEY, F. J., and HAIGH, D. G. (Eds) 'Analogue IC design: the current-mode approach' (Peter Peregrinus Ltd, 1990)

- 7 VITTOZ, E. A., and WEGMANN, G.: 'Dynamic current mirrors', in TOUMAZOU, C., LIDGEY, F. J., and HAIGH, D. G. (Eds) 'Analogue IC design: the current-mode approach' (Peter Peregrinus Ltd, 1990)

- 8 TOUMAZOU, C., HUGHES, J. B., and PATTULLO, D. M.: 'Regulated cascode switched-current memory cell', Electron. Lett., 1990, 26, pp. 303-305

- 9 WEGMANN, G., and VITTOZ, E. A.: 'Analysis and improvements of accurate dynamic current mirrors', IEEE J. Solid-State Circuits, 1990, 25, pp. 699-706

ELECTRONICS LETTERS 13th September 1990 Vol. 26 No. 19

1595